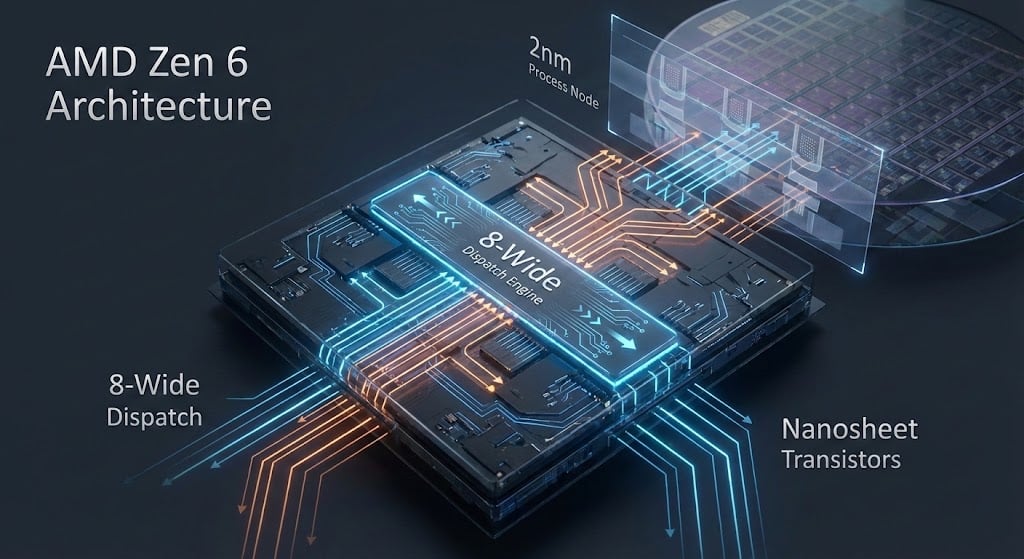

מסמכים טכניים חדשים חושפים את התוכנית השאפתנית של AMD למעבר למנוע עיבוד רחב במיוחד ותהליך ייצור מתקדם, במטרה לשבור את שיאי הביצועים במרכזי הנתונים ובמחשוב האישי

תעשיית השבבים ניצבת בפני נקודת מפנה משמעותית, כאשר פרטים טכניים ראשונים על ארכיטקטורת Zen 6 העתידית של AMD מעידים על שינוי תפיסתי עמוק. בניגוד לשיפורים ההדרגתיים שאפיינו את המעבר בין הדורות הקודמים, הפעם מדובר בתכנון מחדש שנועד להפוך את המעבד למפלצת ביצועים רחבת סרט. הלב הפועם של הארכיטקטורה החדשה, המכונה פנימית Morpheus, מתבסס על מנוע ניתוב הוראות (Dispatch) בעל שמונה נתיבים – קפיצה דרמטית לעומת שישה נתיבים בדור הנוכחי. המעבר למבנה רחב כל כך מאפשר למעבד לטפל בכמות גדולה בהרבה של פעולות בכל מחזור שעון, מה שמציב את AMD במסלול התנגשות ישיר מול ארכיטקטורות הקצה של אפל ואינטל.

ארכיטקטורה רחבה לעידן המחשוב המקבילי

התכנון החדש של Zen 6 אינו מסתכם רק ברוחב הפס. המסמכים הטכניים חושפים כי AMD בחרה באסטרטגיה של תעדוף תפוקה (Throughput) על פני מהירות שעון טהורה בלבד. השימוש בטכנולוגיית SMT (Simultaneous Multi-threading) עובר אופטימיזציה, כך ששני תהליכונים (Threads) יתחרו באופן דינמי על משאבי הניתוב המורחבים. מדובר בהחלטה הנדסית מודעת: בעוד שביצועי הליבה הבודדת עשויים להיות מושפעים במצבים מסוימים, היכולת הכוללת של המעבד להתמודד עם עומסי עבודה מורכבים ורב-תהליכוניים מזנקת מדרגה. כדי לנהל את העוצמה הזו, המעבדים יכללו מערכות ניטור מתקדמות שיאפשרו למפתחי תוכנה לזהות צווארי בקבוק בזמן אמת ולנצל כל נתיב פנוי במנוע העיבוד.

דומיננטיות וקטורית וייצור ב-2 ננומטר

אחד החידושים המרכזיים ב-Zen 6 הוא הדגש חסר התקדים על יכולות וקטוריות וחישובי נקודה צפה, תחומים קריטיים עבור עומסי עבודה של בינה מלאכותית (AI) ולמידת מכונה. הארכיטקטורה תציע תמיכה מלאה בסט ההוראות AVX-512 עם רוחב פס מלא, כולל פורמטים מגוונים כמו FP16 ו-BF16. המטרה ברורה: להפוך את המעבד המרכזי לישות שמסוגלת לבצע חישובים מתמטיים כבדים שבעבר דרשו מאיצים גרפיים ייעודיים. כל זה יתאפשר הודות למעבר לתהליך הייצור ב-2 ננומטר של TSMC, טכנולוגיה המבוססת על טרנזיסטורי Nanosheet (GAA). מעבר זה צפוי להעניק שיפור של כ-15% בביצועים באותה צריכת חשמל, או לחילופין חיסכון של עד 30% באנרגיה.

היעד: 256 ליבות וביצועי קצה בדאטה סנטר

במרכז התחזיות עבור Zen 6 ניצבת סדרת ה-EPYC המכונה Venice, המיועדת למרכזי נתונים. כאן AMD מתכננת לדחוס עד 256 ליבות עיבוד על גבי שבב בודד, הישג שיהפוך את המעבדים הללו לעמוד השדרה של תשתיות הענן המודרניות. השימוש במבנה צ'יפלט (Chiplet) מתקדם יאפשר שילוב בין ליבות ביצועים (Zen 6) לבין ליבות יעילות (Zen 6c), תוך ניצול תושבת ה-SP7 החדשה שתתמוך בצריכת חשמל גבוהה במיוחד עבור עומסי מחשוב קיצוניים. המעבר ל-Zen 6 מסמן את הרגע שבו AMD מפסיקה לרדוף אחרי השוק ומתחילה להכתיב את הקצב, עם ארכיטקטורה שנבנתה מהיסוד עבור עולם שבו המידע הוא המשאב היקר ביותר.